解读:IC封装行业的最新技术和市场趋势

SiP技术的优势在于:

融合多种技术

能够在一个封装中集成多种技术和组件,例如组合MEMS和CMOS。这种组合对于传统IC是不可能的。虽然MEMS和CMOS器件有许多相似之处,但也有一些关键区别。首先是需要一种方法将感知传递给MEMS器件,因为它们必须与环境相互作用;其次,MEMS器件的扩展方式与CMOS不同工艺的扩展方式不同。

采用多种工艺

SiP技术提供的集成对可穿戴设备、智能灯或智能家居等应用特别有价值,因为这些产品的空间和尺寸非常重要。从实际应用看,SiP设计方案融合了晶圆级封装(WLP)、2.5D或3D结构、倒装芯片(flip-chip)、引线键合、封装体叠层(package-on-package)等工艺;还可以嵌入无源器件、共形屏蔽、滤波器和天线。

典型IoT方案的几种SiP封装

融合MEMS传感器

MEMS传感器需要与环境交互以进行声音、光或气体检测。使用MEMS封装通常要从QFN封装迁移到基于层压板的封装。层压板设计可以采用腔基封装或混合腔封装,其中封装的一半是模压的,另一半是为MEMS器件提供一个空腔。这种模压器件更能承受恶劣的环境。

实现IoT标准化封装

目前,MEMS、传感器及IoT器件的封装设计还很零散。设计人员希望多个项目重用相同的封装,即使这些封装并不总是与特定应用兼容。MEMS、传感器封装的标准化将有助于降低成本和加快MEMS的采用,增强制造商将新产品推向市场的信心。

FOWLP实现极致性能

摩尔定律在工艺技术上似乎已走到了尽头,所以先进封装技术正在接棒,如扇出晶圆级封装(FOWLP)就可以提高组件密度和性能,有助于解决芯片I/O限制。不过,成功的关键是从芯片设计开始。

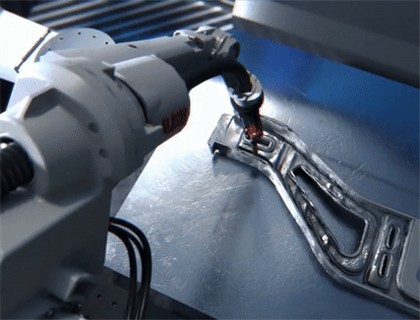

现在,FOWLP已经在移动设备的批量生产中使用。其封装过程包括将单个芯片安装在称为重分布层(RDL)的中间层基板上,该层提供芯片之间的互连以及与I/O焊盘的连接,所有这些芯片都封装在一个模压成型中。

所谓扇出封装,是将连接件扇出到芯片表面,以便实现更多外部I/O,使用环氧模压化合物完全嵌入片芯(die),因此不需要晶圆植球、熔剂、倒装芯片组装、清洗、底填料注入和固化等工艺流程。这反过来又消除了中间层,并使异构集成的实现更加简单。

扇出技术可以提供比其他封装类型更多I/O的小尺寸封装。早在2016年,苹果就凭借台积电(TSMC)的集成扇出(integrated fan-out,InFO)晶圆级封装技术,将其16nm A10应用处理器与移动DRAM集成到iPhone 7内部的一个封装中,为应用处理器提供更好的热管理。TSMC的InFO使苹果实现了非常薄的封装体叠层(PoP,Package-on-Package)。

TSMC的InFO技术

InFO平台的再分布层技术将硅片直接连接到PCB层,而无需另一层基板。台积电设计的互连通孔(TIV)可以提供支柱,使用混合垂直和水平互连技术连接不同的硅片或组件。InFO体现了其短垂直和长水平连接之间的连接,加速了信息的传播。

作为对WLP的改进,FOWLP技术可以提供更多与硅片芯的外部接点。它将芯片嵌入环氧模压料中,然后在晶圆表面制造高密度RDL和锡球,形成一个重组晶圆。

通常,它首先将前道处理过的晶圆切成单独的片芯,然后将片芯在载体结构上隔开,其空隙被填满形成一个重组晶圆。FOWLP在封装和应用板之间提供了大量的连接。此外,基板基本上比片芯大,因此片芯间距更为宽松。

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

限时免费下载立即下载 >>> 2024“机器人+”行业应用创新发展蓝皮书

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论