解读:IC封装行业的最新技术和市场趋势

传统多片芯封装与FOWLP

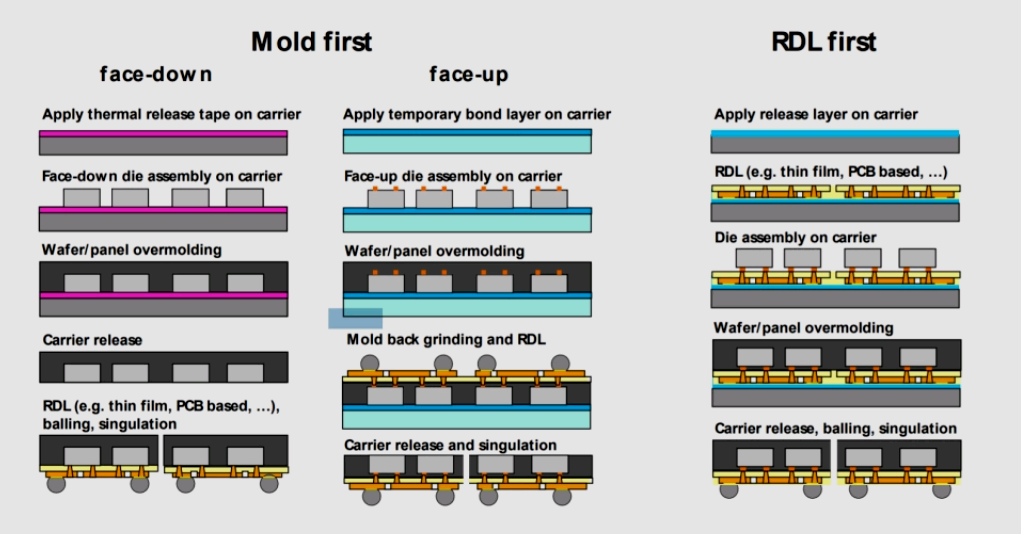

FOWLP有几种变体,每种都使用稍有不同的制造步骤。FOWLP组件可以使用模压优先(mold-first)流程创建,片芯面朝下或面朝上安装,或者使用RDL优先(RDL-first)组件。

模压优先方法

片芯使用临时粘合层或热释放层连接到载体上,然后将其模制到封装中。如果片芯面朝下安装,接下来的步骤是释放临时层,连接RDL,形成完成封装的焊球。如果片芯面朝上安装,则需要一些附加步骤。

首先,单个片芯I/O连接必须通过在其上添加铜柱来扩展,然后再进行二次成型。成型后,嵌条的背面必须接地,在连接RDL和形成焊球之前露出支柱。

RDL优先方法

RDL使用临时释放层连接载体,而片芯连接到RDL。然后是组装成型、载体释放、焊锡球成型。这两种方法的最后一步都是将组件分开,使这些组件整体形成单独的器件。

FOWLP技术的两种方法

这些方法具有不同的成本和性能权衡。在成本方面,模压优先面朝下方法避免了制作铜柱和研磨,因此制造成本较低;最适合低I/O数的应用;但是,存在着片芯移位、晶圆翘曲等问题,限制了在复杂多芯片封装中的应用。

面朝上的方法减少了这些问题,并在热管理方面有优势,因为芯片背面完全暴露,有利于散热。

在性能方面,与其他两种方法相比,面朝下的方法的连接路径更短。这两种方法都有铜柱,可以将连接延伸到RDL,同时在芯片下有一层材料,增加了连接之间的寄生电容,从而影响了其高频性能。

2.5D到3D IC封装的关键是TSV

在2.5D封装中,片芯采用堆叠或并排放置在基于硅通孔(TSV)的中间层顶部。底部的中间层提供芯片之间的连接。2.5D封装技术是传统2D IC封装技术的一个进步,它使迹线和空间更加精细。

2.5D封装通常用于高端ASIC、FPGA、GPU和内存。2008年,Xilinx将其大型FPGA分成了四个更小、良率更高的芯片,并将这些芯片连接到一个硅中间层上,从而诞生了2.5D封装,最终成为流行的高带宽内存(HBM)处理器集成。

TSV连接的功能完整的3D封装

在3D IC封装中,逻辑片芯堆叠在一起,通过铜TSV在硅芯片之间实现垂直互连,并使用有源中间层连接片芯。与通过导电凸点或TSV将元件堆叠在中间层上的2.5D不同,3D IC封装采用多层硅晶圆并通过TSV将元件堆叠在一起。

TSV是2.5D和3D封装解决方案中的一项关键技术,它提供了一种穿过片芯硅晶圆的垂直互连。这种封装是以晶圆形式制造的,里面填充了铜。TSV是一种穿过芯片整个厚度或基板延伸的长通孔电气连接,它创建了从芯片一侧到另一侧的最短路径。然而,TSV除了自身显著的电气特性外,还对其附近的器件和互连的电气行为产生间接影响。

为了精确地模拟一个2.5D/3D异构系统,设计者需要从这些2.5D/3D元素的物理结构中提取精确电参数的工具,然后将这些参数输入行为仿真器。利用完整组件装配的3D数字孪生模型,设计者可以准确地提取出2.5D和3D模型中的寄生性,以分析性能和适当的协议遵从性。

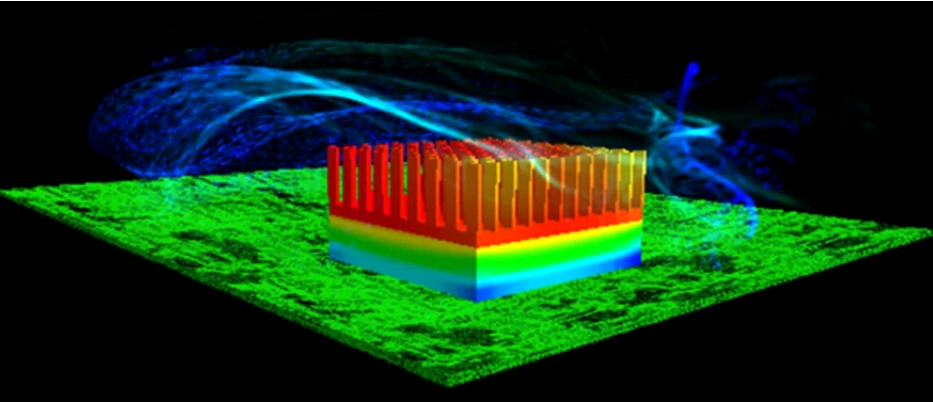

值得注意的是,2.5D和3D堆叠都会产生各种偶然的物理应力,例如在安装过程中基板翘曲和碰撞引起的应力。设计人员必须能够分析这种芯片封装交互作用引起的应力及其对器件性能的影响。一旦封装接近完成,需要导出精确的3D封装热模型,以便在详细的PCB和全系统热分析中使用,进而对系统外壳进行最终调整,并优化自然和/或强制冷却。

3D IC封装的热仿真

最新活动更多

-

3月27日立即报名>> 【工程师系列】汽车电子技术在线大会

-

4月1日立即下载>> 【村田汽车】汽车E/E架构革新中,新智能座舱挑战的解决方案

-

4月23日立即报名>> 【在线会议】研华嵌入式核心优势,以Edge AI驱动机器视觉升级

-

4月25日立即报名>> 【线下论坛】新唐科技2025新品发布会

-

4月30日立即参与 >> 【白皮书】研华机器视觉项目召集令

-

限时免费下载立即下载 >>> 2024“机器人+”行业应用创新发展蓝皮书

分享

分享

发表评论

请输入评论内容...

请输入评论/评论长度6~500个字

暂无评论

暂无评论